**32**<sup>nd</sup> Annual **INCOSE**

international symposium

hybrid event

Detroit, MI, USA

June 25 - 30, 2022

# A Platform for MBSE-Enabled, Digitally Threaded, Electronics Design and Verification

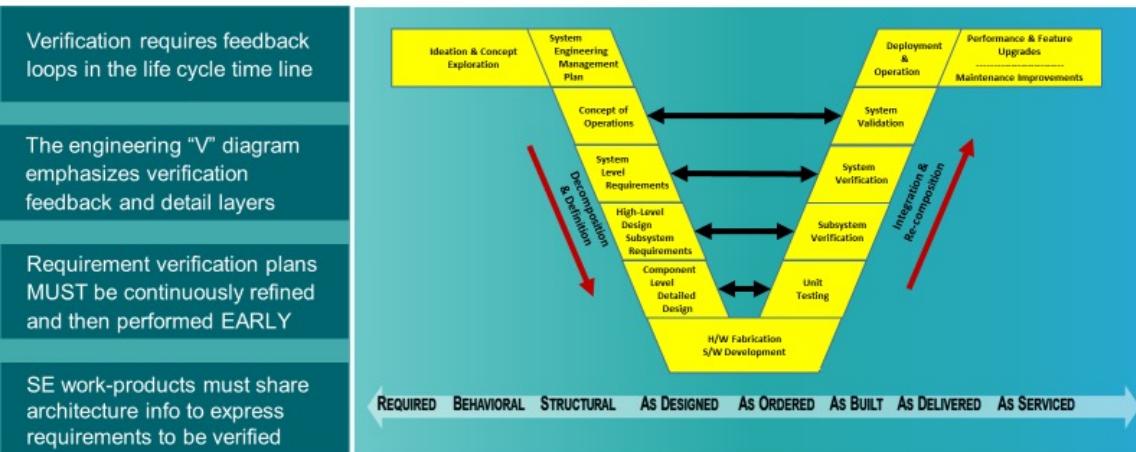

REQUIRED BEHAVIORAL STRUCTURAL AS DESIGNED AS ORDERED AS BUILT AS DELIVERED AS SERVICED

### Systems Engineering

- Begins at the conceptual design phase, continuing throughout the life cycle

- Defines and validates requirements to meet user needs

- Designs, analyzes and verifies a system to meet the requirements

**Before there was CAD/CAE, there was Systems Engineering. Many types of SE documents and diagrams were produced, maintained and shared manually.**

**If MBSE is to be CAD/CAE for SE, are we there yet?**

Page 2

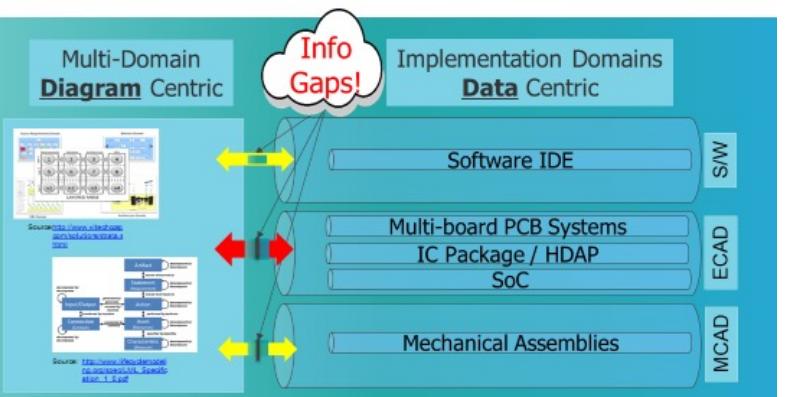

Current Electronics Status: MBSE-driven Architecture is NOT SHAREABLE;

Most SE diagrams are not intuitive. Domain engineers are not fluent in them.

Most diagrams are not stored as data elements in enterprise level database repositories.

Gaps exist which restrict the flow of information. The ECAD gap is the most severe.

ECAD has sub-domain decomposition layers and the deepest verification challenge.

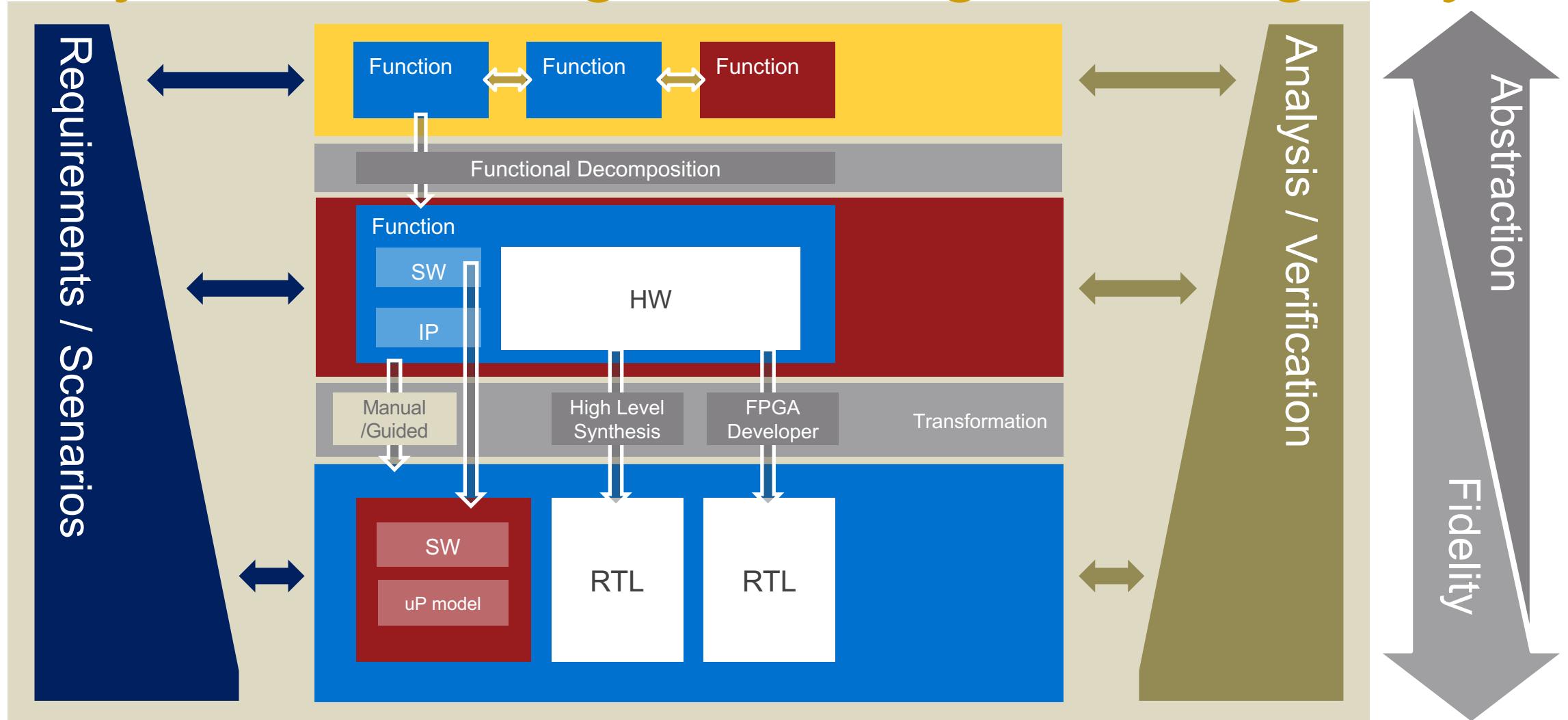

### Engineering "V" – Emphasis on Continuous Verification Levels

Page 3

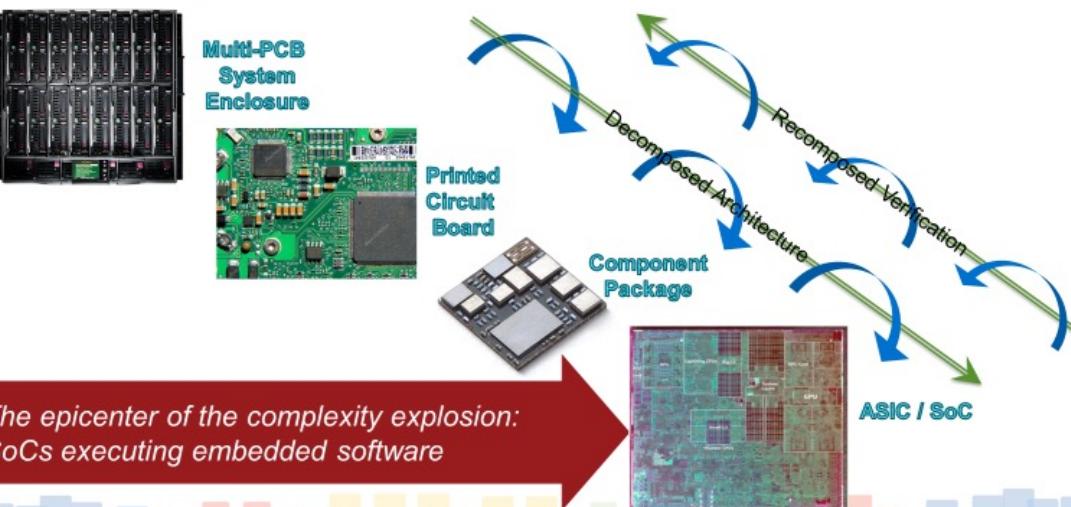

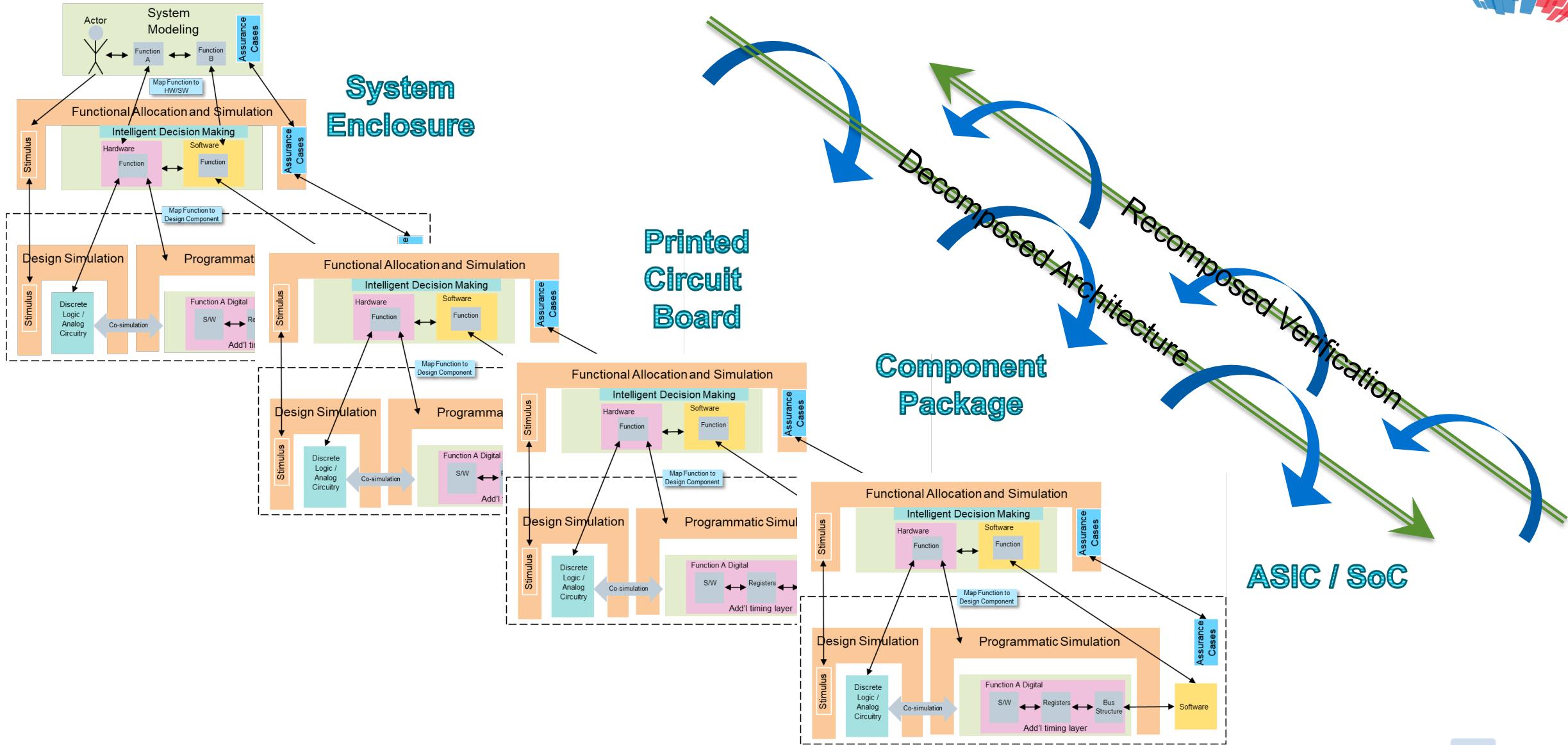

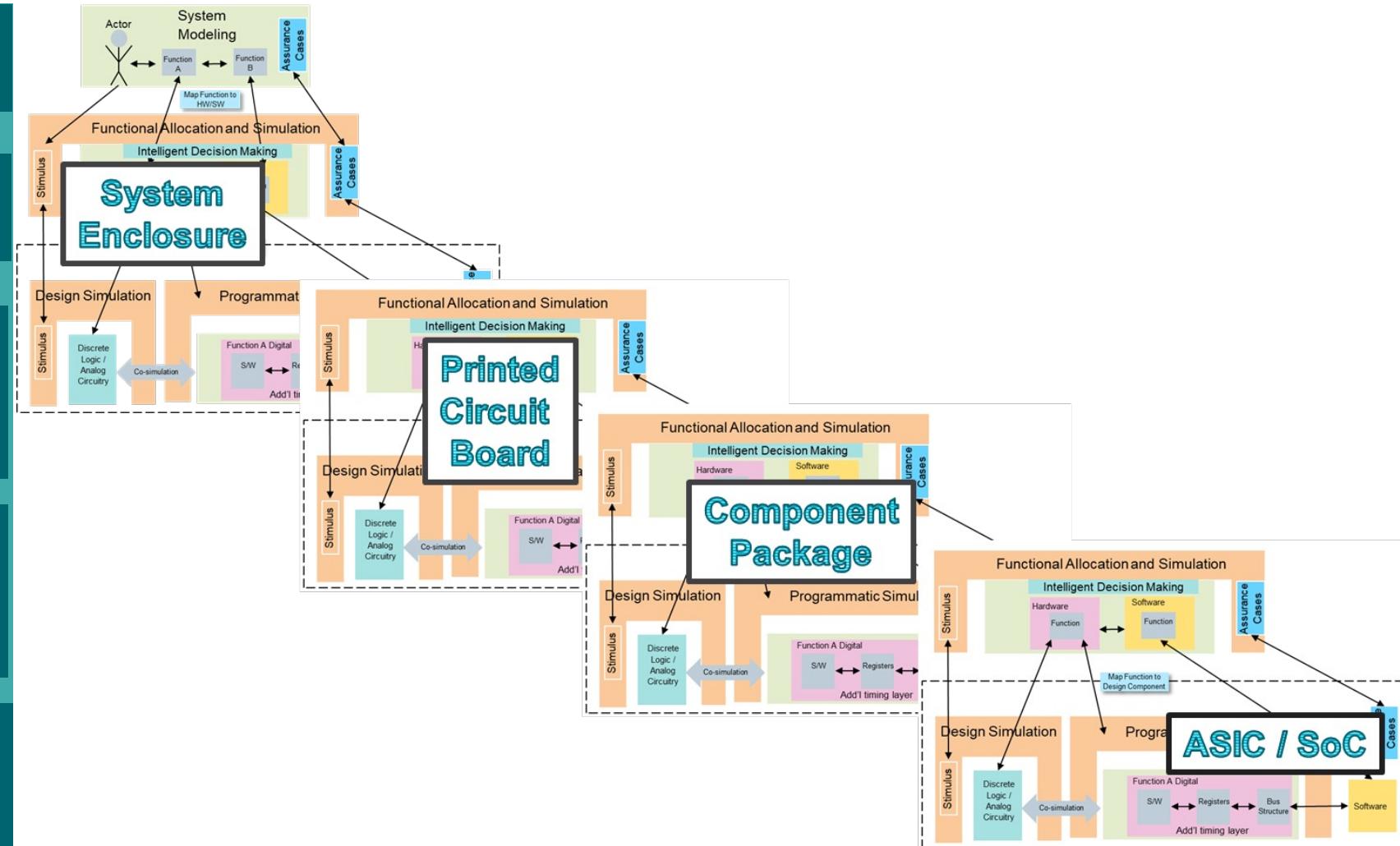

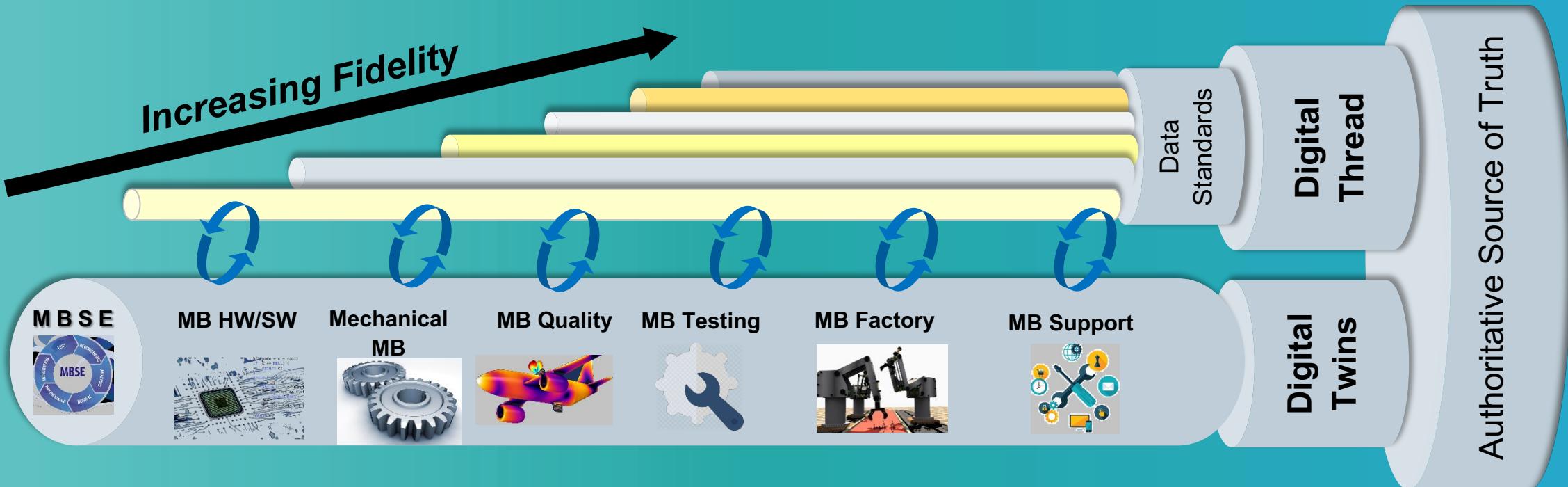

Electronics Requires Continuous Decomposition and Verification to Realize "System-to-Silicon" Verification

Page 2

# Risks of Functional Allocation Overloading Electronics

*Then*

*Now*

*Soon?*

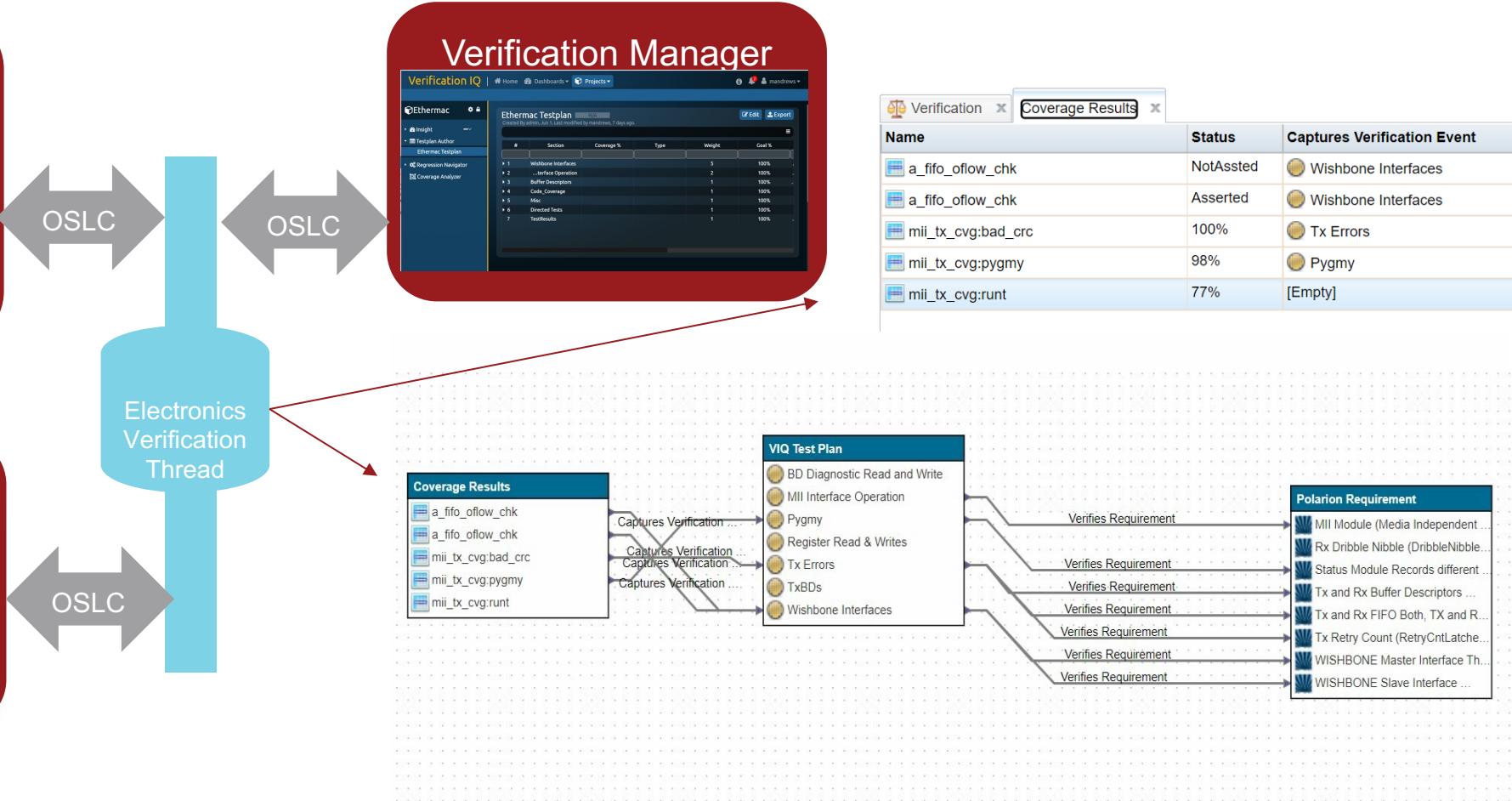

# Future State: Commonality Across Workflows, System-to-Silicon

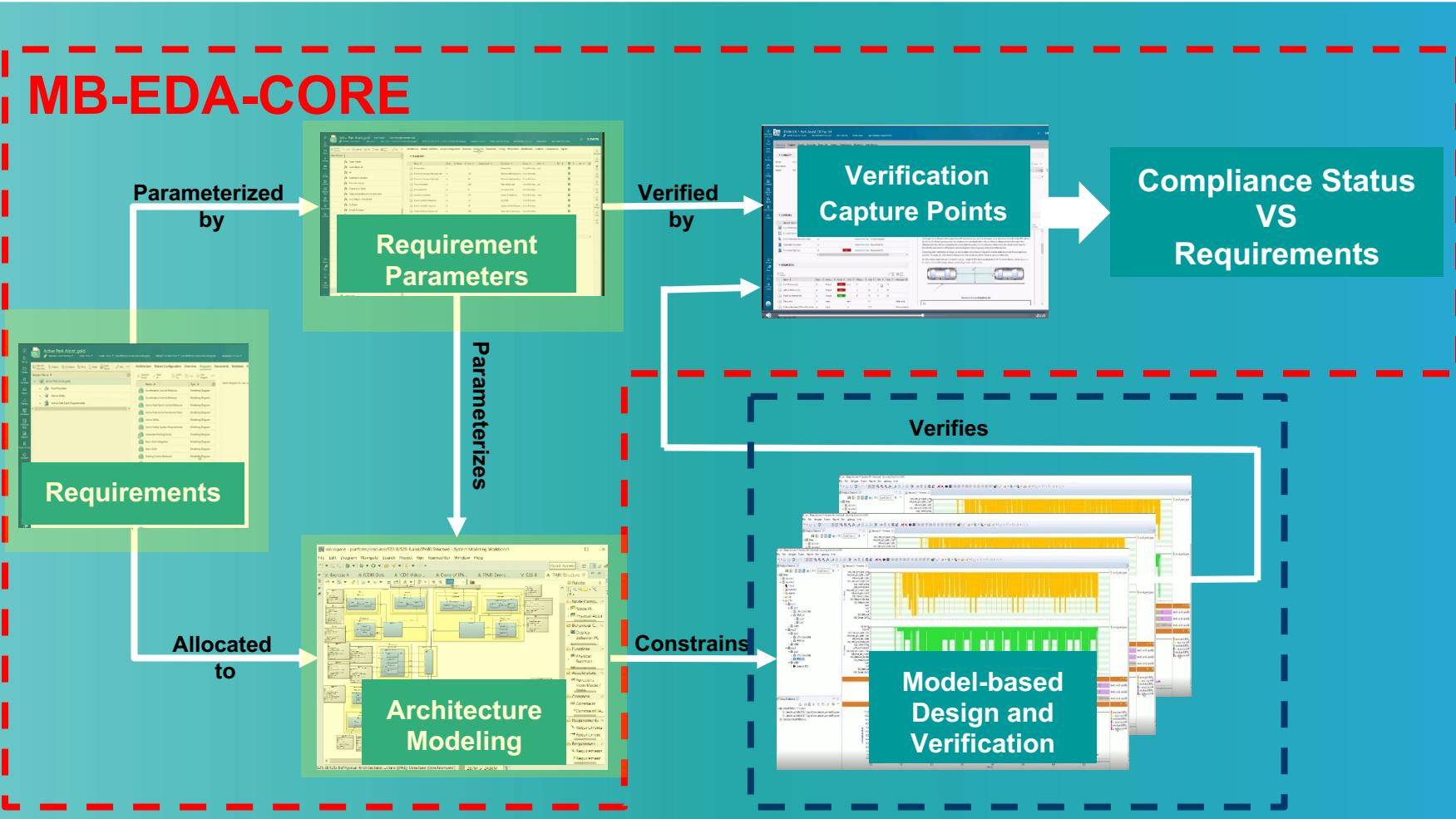

# A Solution Pattern Implementation Consists of both Domain Independent (ASoT) and Domain/Sub-domain Dependent Workflow Components and Tools

Enabling the ASoT can be domain independent and non-ECAD specific

Domain specific tools can potentially be any design and verification toolset

Domain specific tools will likely need automation to increase efficiency / reduce cycle time

Bottom-up approach:

Implement VCPs for what is simulated today

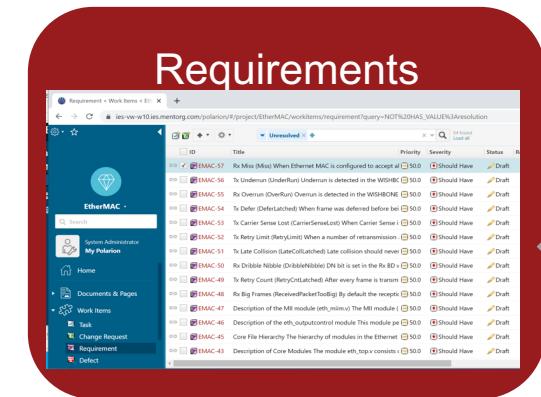

# Requirement Allocation Example

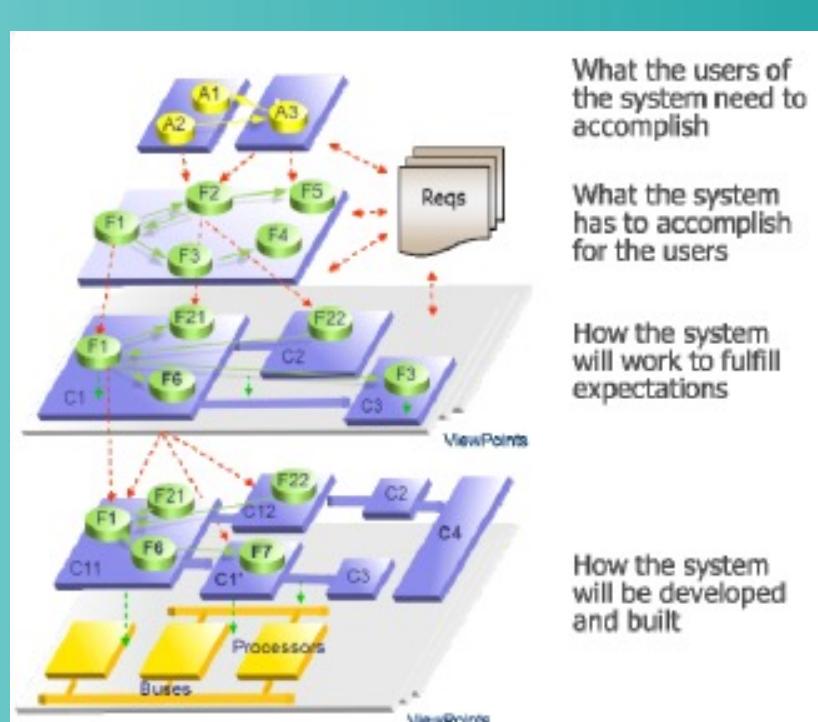

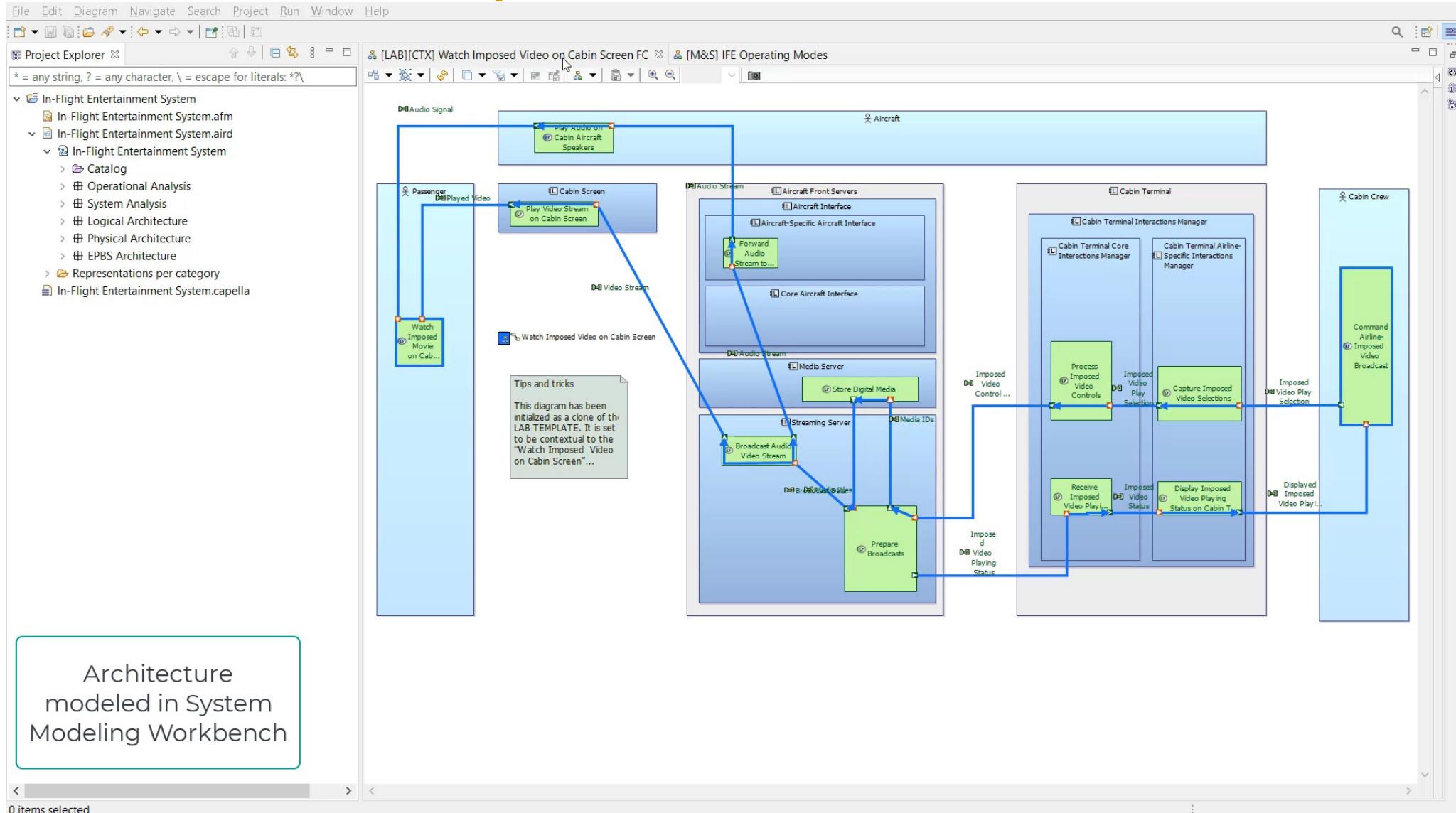

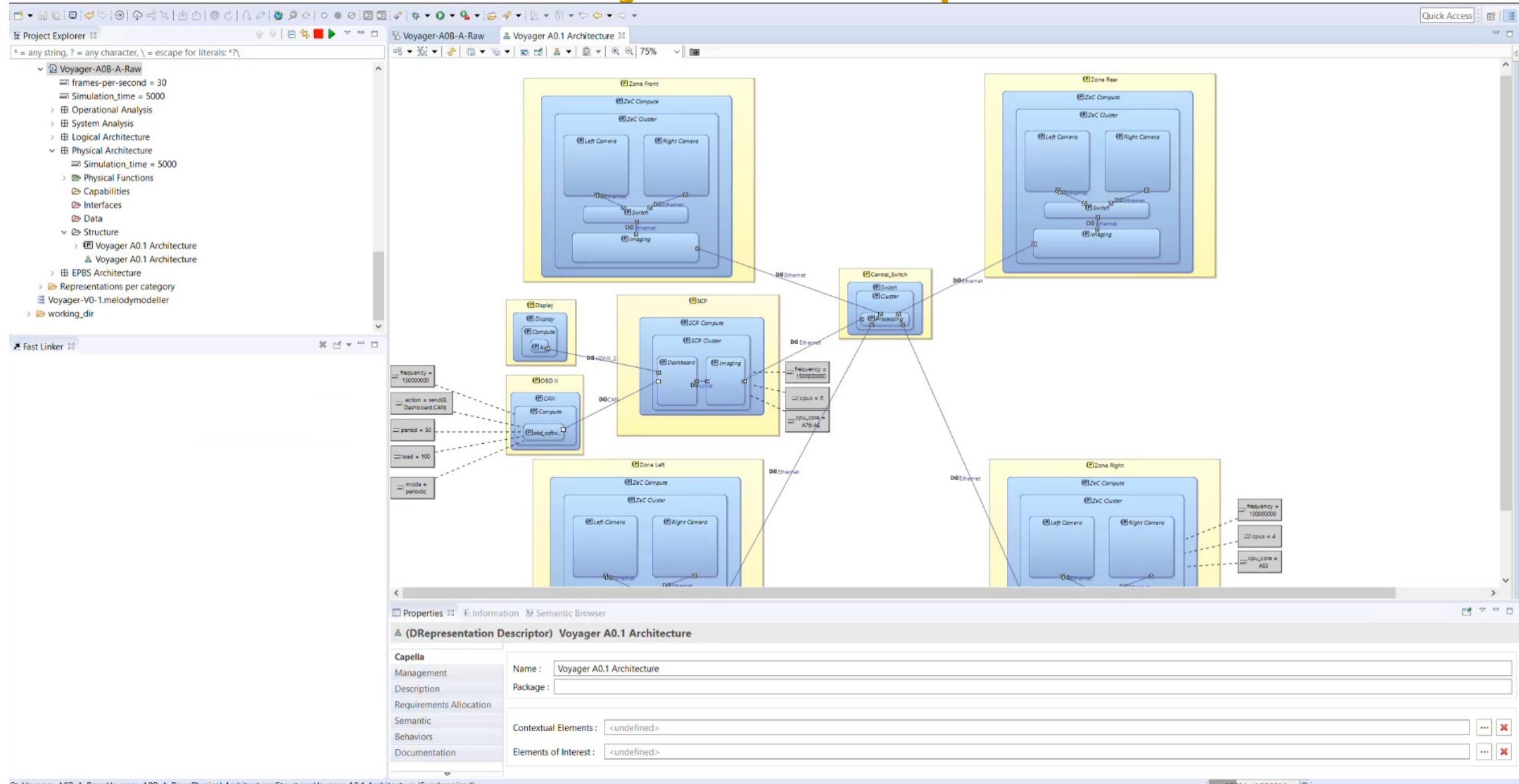

# ARCADIA/Capella Uniquely Addresses Continuous Decomposition

Siemens selected

Arcadia/Capella as basis for

System Modeling Workbench

Most modern method and

tooling with most advanced

refinement capabilities

CAD/CAE style of underlying

data model

Guides the user to assure

models are correct and well

formed

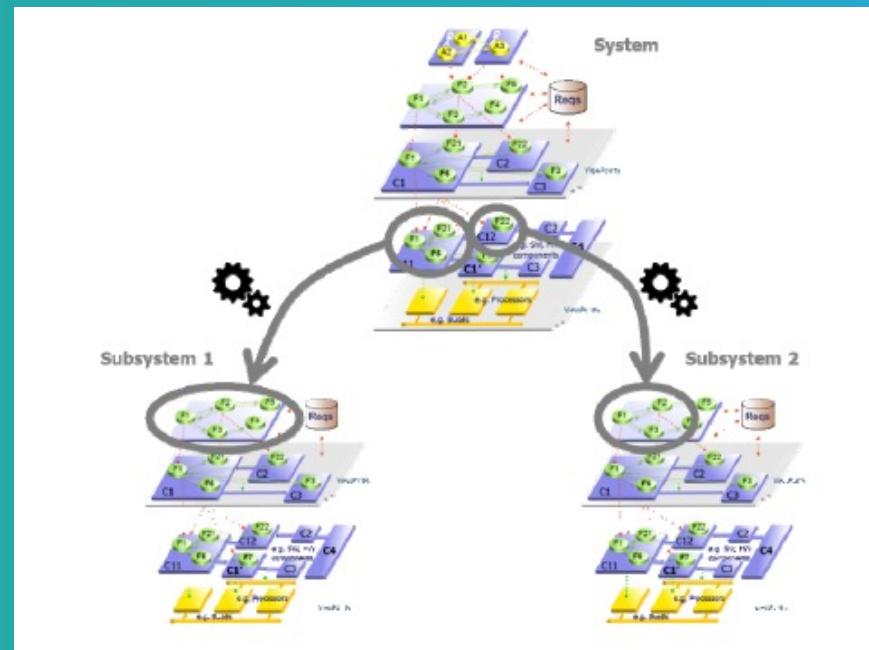

# Sub-system transition

# Path to Standards Conformance: Working toward Capella Generative SysML V2 Concrete Syntax

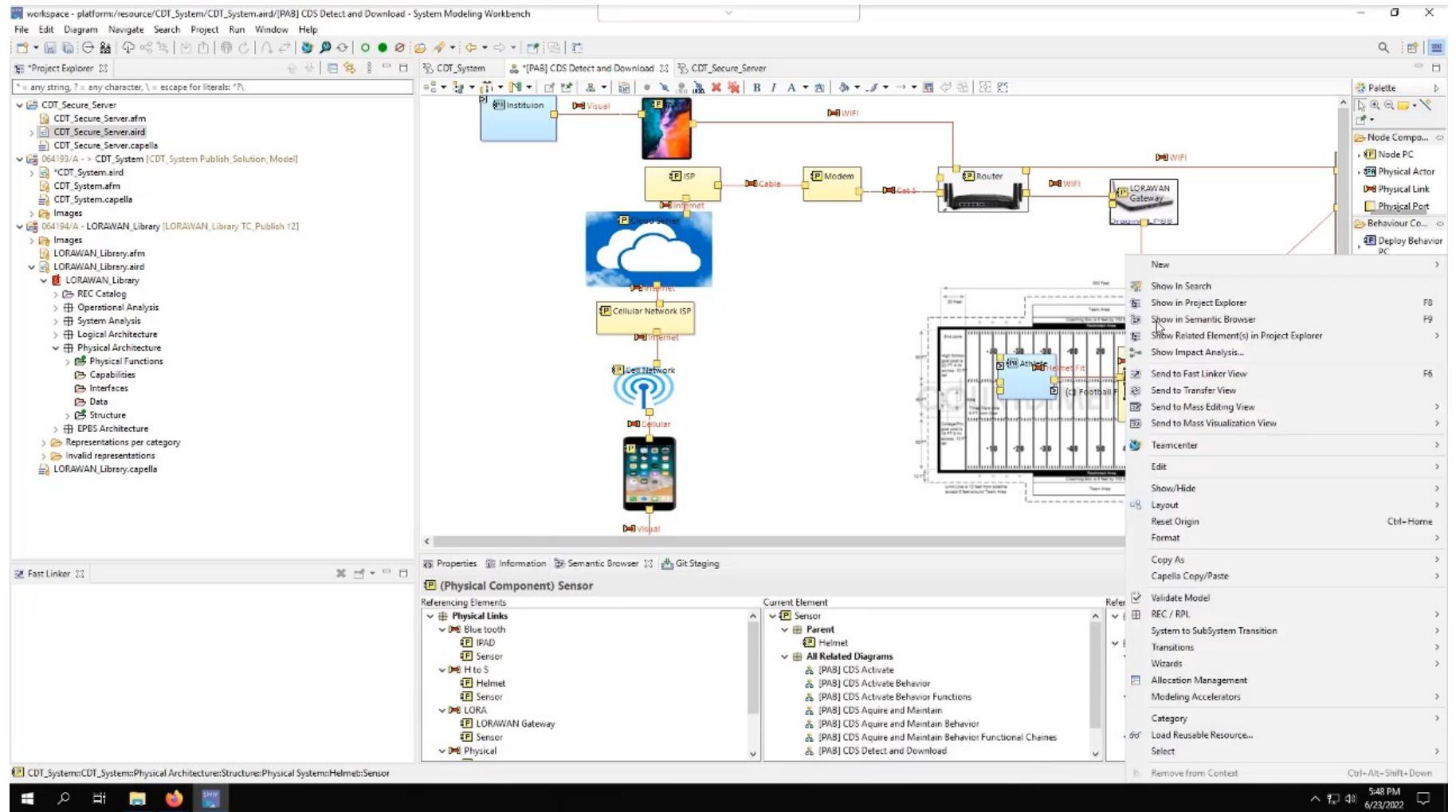

File Edit Diagram Navigate Search Project Run Window Help

Package Explorer [LAB] Camera Camera-Capella.sysml Camera-Capella.sysml PictureTaking.sysml

Camera Camera.afm Camera.aird Camera.melodymodeller Camera-SysMLV2 Camera-Capella.sysml PictureTaking.sysml fr.obeo.gen.capella2sysml2 JRE System Library [JavaSE-1.8] Plug-in Dependencies src fr.obeo.gen.capella2sysml2 fr.obeo.gen.capella2sysml2.main Generate.java generate.mtl gen META-INF tasks build.properties sysml.library

part def Camera {

import PictureTaking::\*;

perform takePicture[\*] as PictureTaking::takePicture;

part FocusingSubsystem {

perform takePicture::focus;

}

part imagingSubsystem {

perform takePicture::shoot;

}

}

Logical Architecture

Generative

SysML v2 concrete syntax

# SysML V2 Example

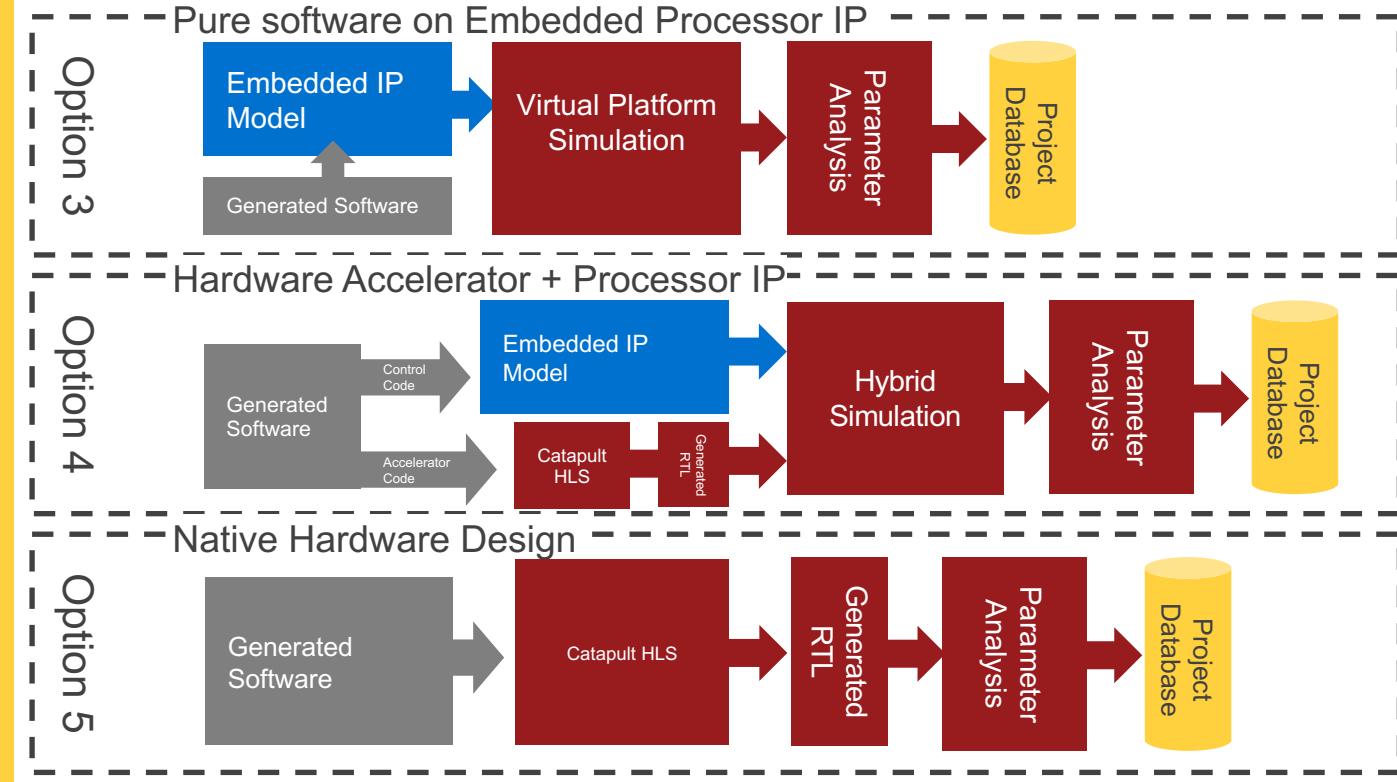

# Allocatable Electronics Performance Levels

1. SoC INDEPENDENT s/w

2. SoC Dependent S/W

(e.g. CUDA, Assembler)

3. Embedded Processor IP

Dependent S/W

4. H/W Accelerator Plus

Embedded Processor IP and

Dependent S/W

5. Native H/W Acceleration

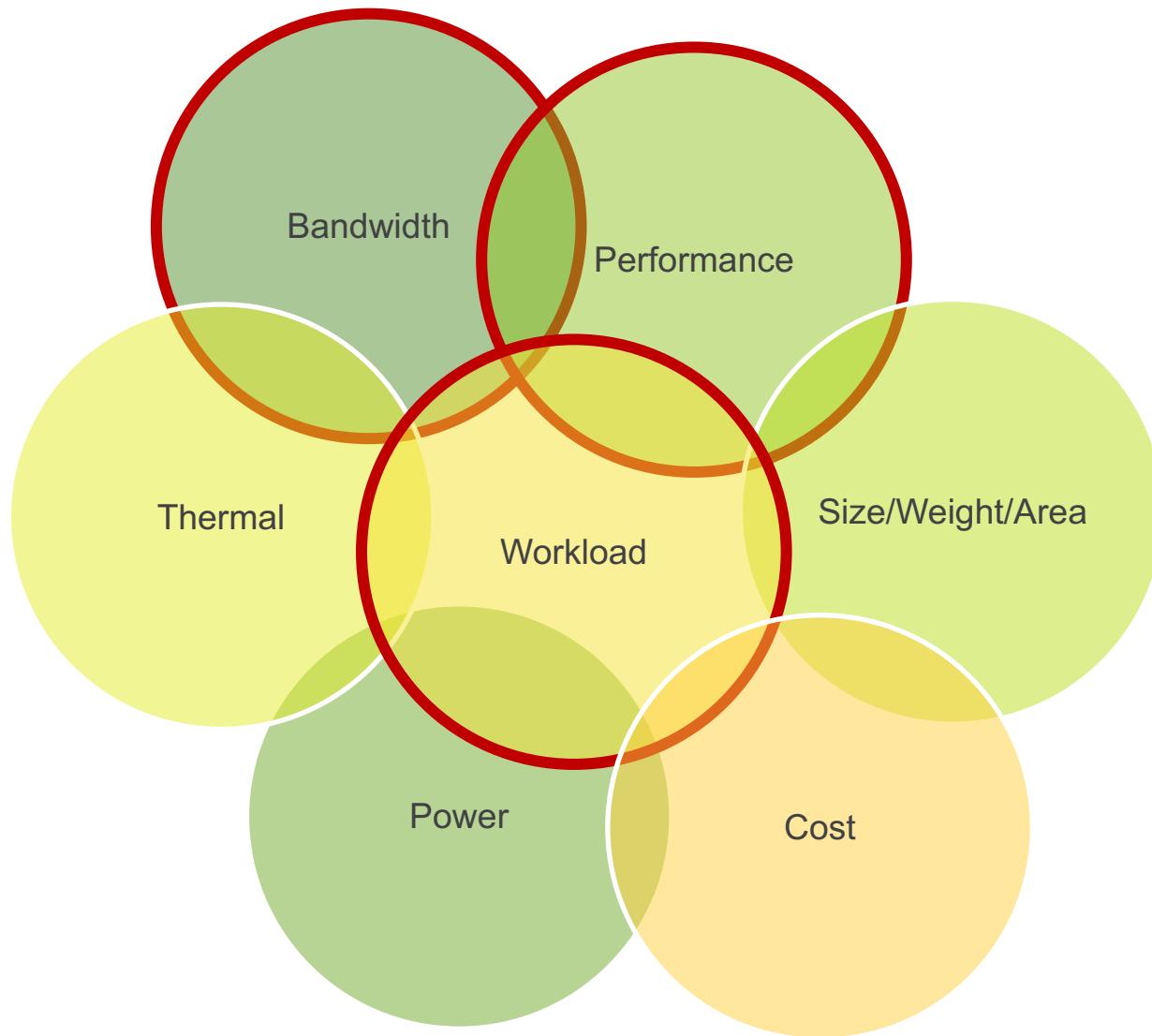

# Architecture Design Options are Expanding Exponentially

Approximate the

electronics to

narrow the

tradeoff space

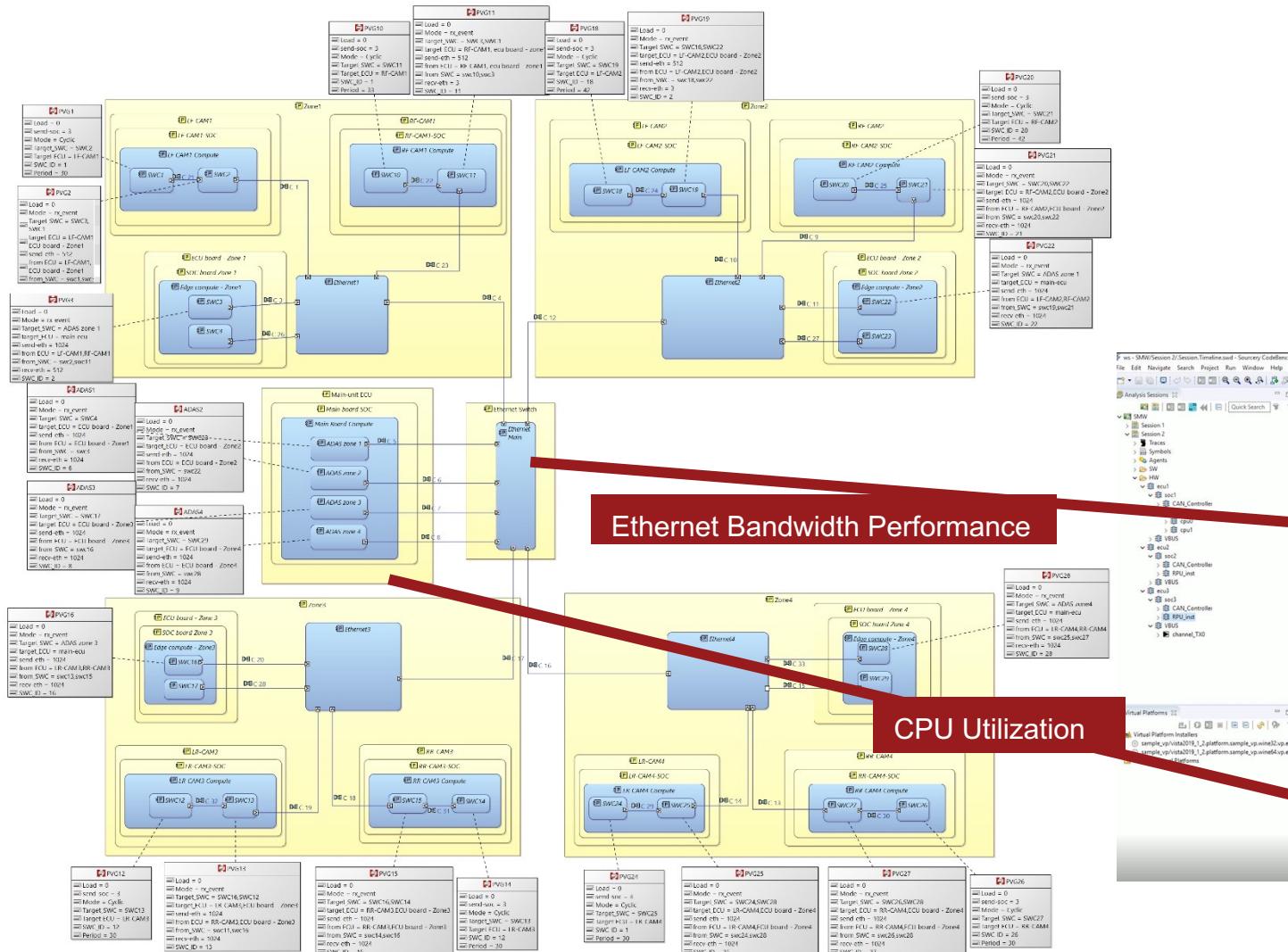

# Architecture Exploration by Transaction Level Simulation; System-to-Silicon

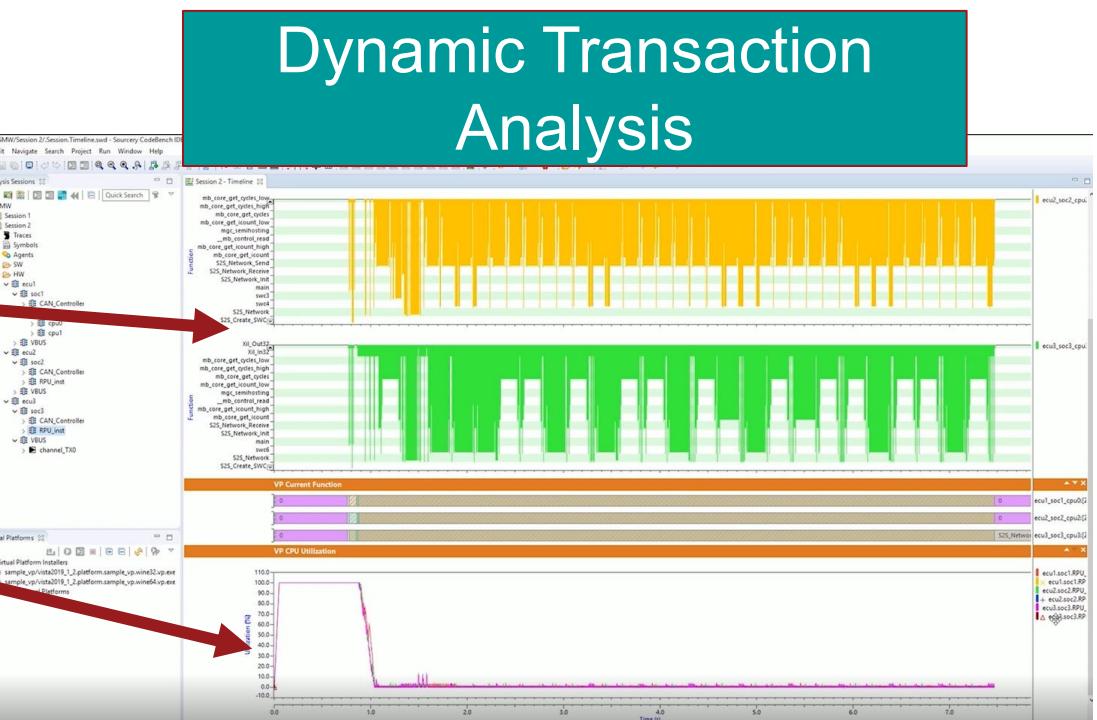

# Dynamic Transaction Analysis

# Architecture Analysis Example

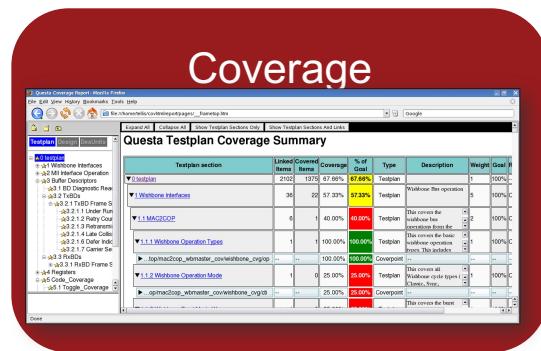

# Verification Capture Point Example

▼ PARAMETERS

Hide Unused

Start Edit

| Name                           | Rev... | Releas... | Description              | Source | Usage | Result | Units | Measu... | Goal | Min | Max |

|--------------------------------|--------|-----------|--------------------------|--------|-------|--------|-------|----------|------|-----|-----|

| Max speed 1.1.1 Speed          | A      |           | Speed                    | Output | Pass  | 72     | 60    | 10       | 75   |     |     |

| Network bandwidth 1.1.4 B...   | A      |           | Bandwidth                | Output | Fail  | 180    | 65    | 20       | 80   | 80  |     |

| Time to object 1.1.2 Time t... | A      |           | Time to object detection | Output |       | sec    | 80    | 10       | 100  |     |     |

| VnVParaDefDouble 1.1.2 Ti...   | A      |           | Time to object detection | Output |       |        | 50    | 40       | 100  |     |     |

▼ PARAMETERS

Hide Unused

Start Edit

| Name                           | Rev... | Releas... | Description              | Source | Usage | Result | Units | Measu... | Goal | Min | Max |

|--------------------------------|--------|-----------|--------------------------|--------|-------|--------|-------|----------|------|-----|-----|

| Max speed 1.1.1 Speed          | A      |           | Speed                    | Output | Pass  | 72     | 60    | 10       | 75   |     |     |

| Network bandwidth 1.1.4 B...   | A      |           | Bandwidth                | Output | Pass  | 60     | 65    | 20       | 80   |     |     |

| Time to object 1.1.2 Time t... | A      |           | Time to object detection | Output |       | sec    | 80    | 10       | 100  |     |     |

| VnVParaDefDouble 1.1.2 Ti...   | A      |           | Time to object detection | Output |       |        | 50    | 40       | 100  |     |     |

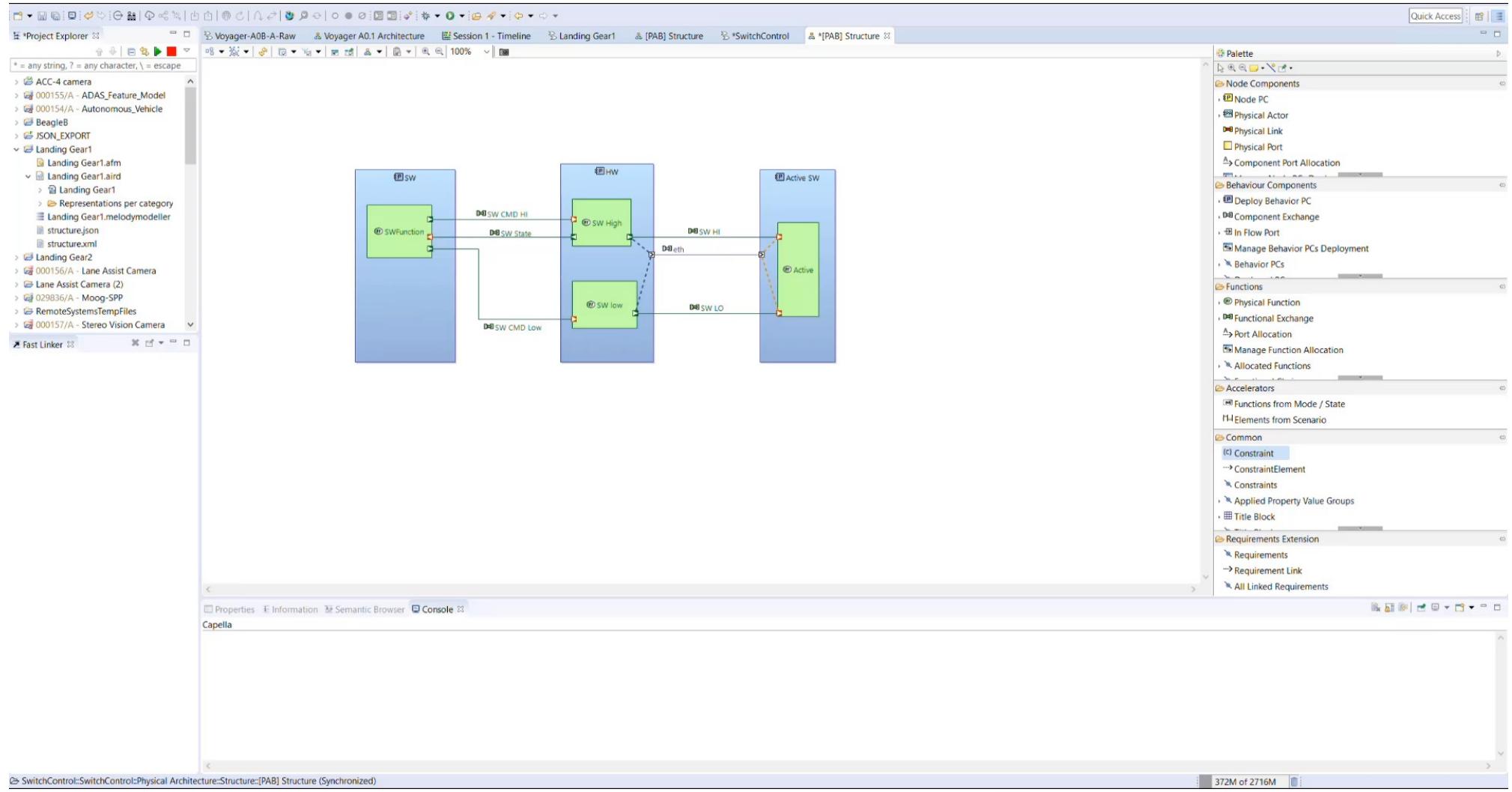

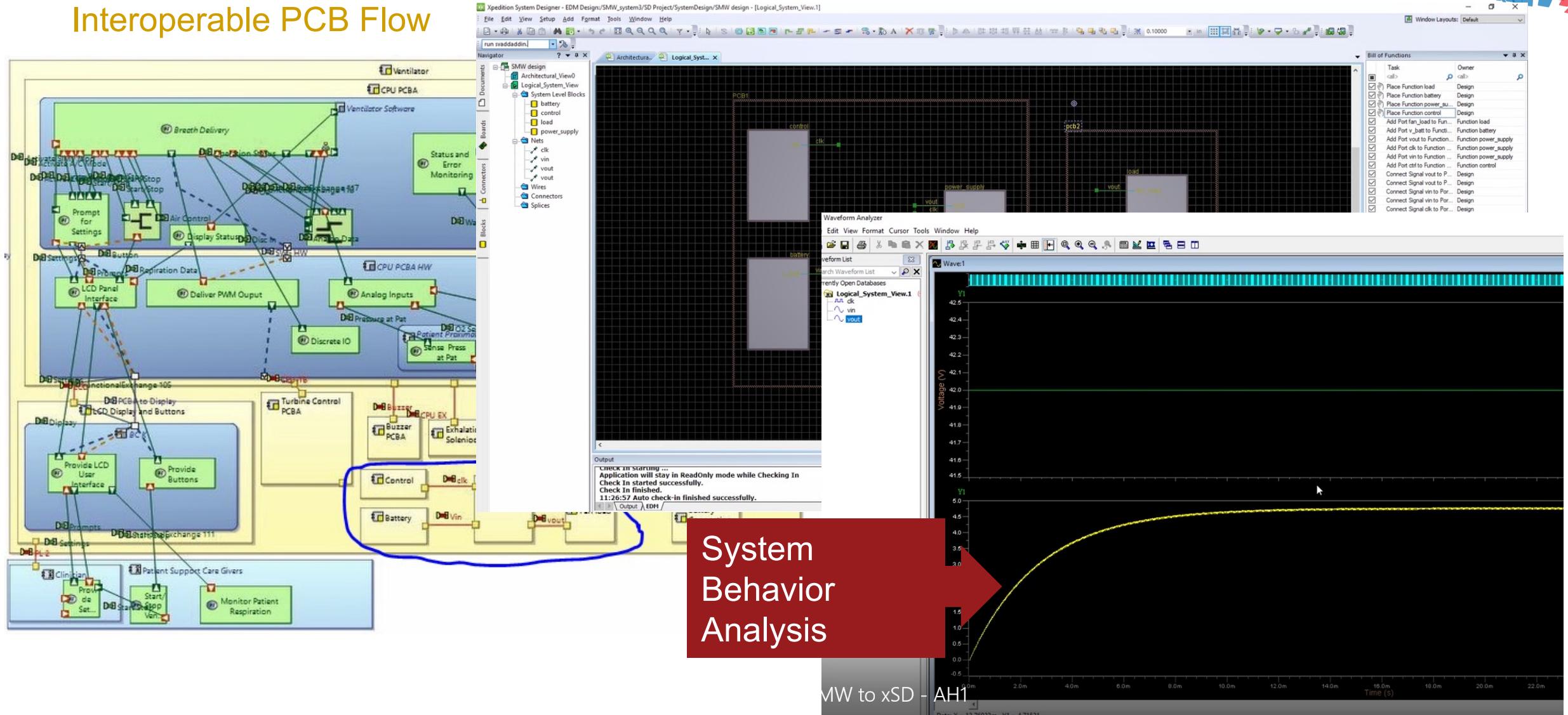

## Architecture Implementation: Interoperable PCB Flow

# PCB Design Example

Project Explorer: Voyager-A0B-A-Raw, Voyager A01 Architecture, Session 1 - Timeline, Landing Gear1, [PAA] Structure, \*SwitchControl, \*[PAB] Structure

Workflow of SwitchControl

- Operational Analysis

- System Analysis

- Logical Architecture

- Physical Architecture

- EPBS

Define Stakeholder Needs and Environment

Capture and consolidate operational needs from stakeholders

Define what the users of the system have to accomplish

Identify entities, actors, roles, activities, concepts

Formalize System Requirements

Identify the boundary of the system, consolidate requirements

Define what the system has to accomplish for the users

Model functional dataflows and dynamic behaviour

Develop System Logical Architecture

See the system as a white box

Define how the system will work so as to fulfill expectations

Perform a first trade-off analysis

Develop System Physical Architecture

How the system will be developed and built

Software vs. hardware allocation, specification of interfaces, deployment configurations, trade-off analysis

Formalize Component Requirements

Manage industrial criteria and integration strategy: what is expected from each designer/sub-contractor

Specify requirements and interfaces of all configuration items

Workflow | Documentation | Operational Analysis | System Analysis | Logical Architecture | Physical Architecture | EPBS

Properties | Information | Semantic Browser | Console

Capella

Go to page Operational Analysis

375M of 2716M

How Do You Digitally Thread Design Verification?

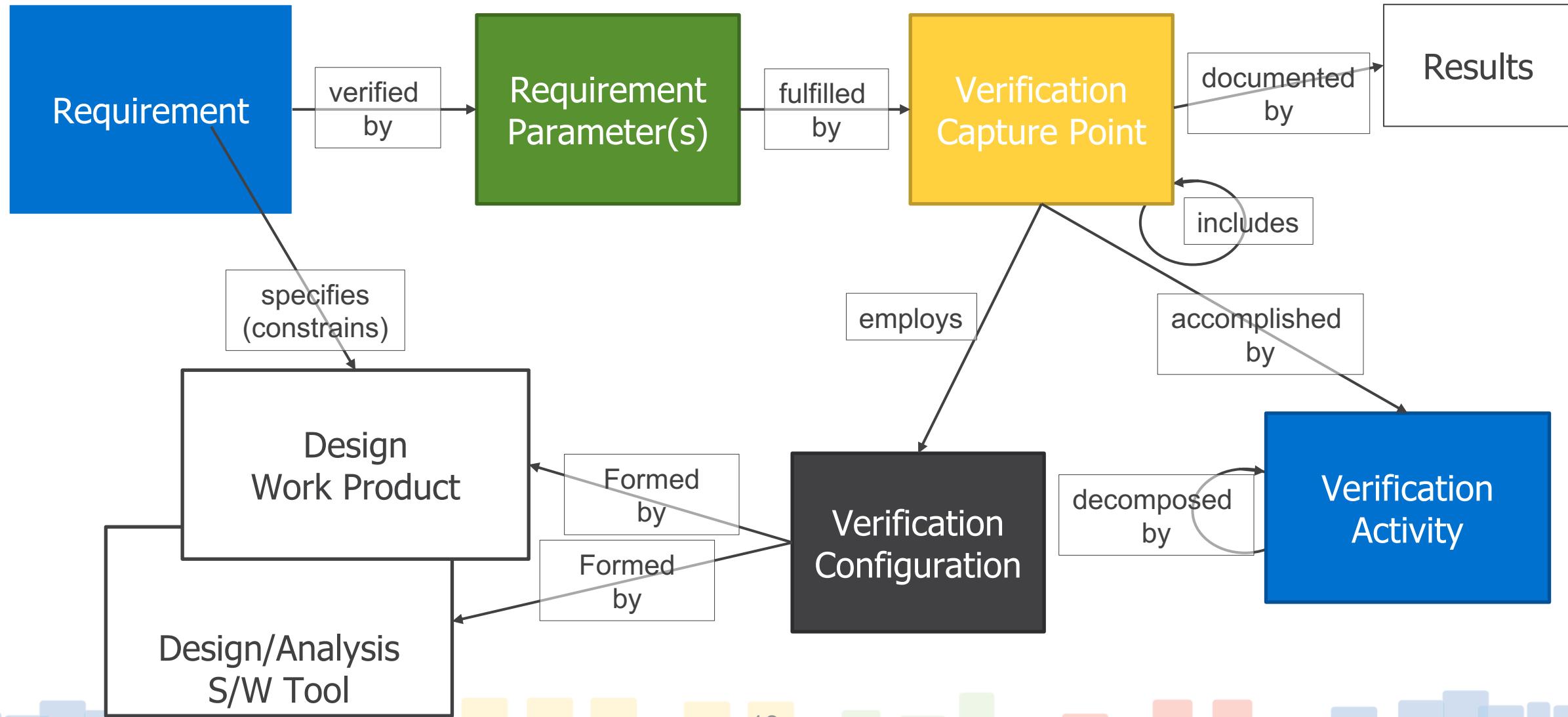

# Verification Capture Point (VCP) Metamodel

# Creating a Verification Thread

# Digital Transformation is Enabled by Digital Twinning and Threading

**Digital Thread:** The authoritative technical data providing decision makers the right data at the right time across the system life cycle

**Digital Twin:** An integrated digital simulation, enabled by digital threading

# Hybrid Twinning in the Digital Design Cycle

# Automated Design Synthesis and Analysis

## Algorithmic Functions Allocated for Implementation

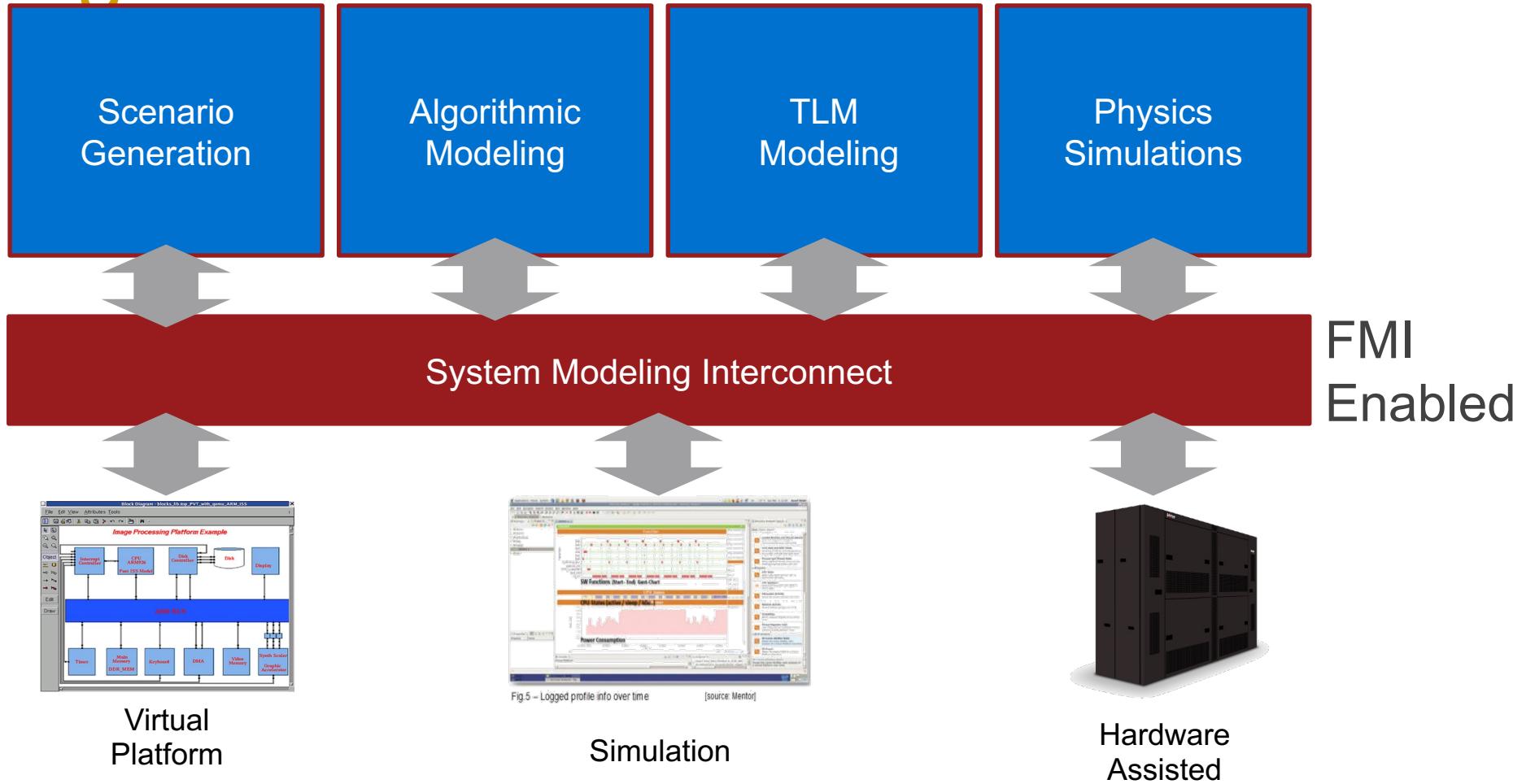

# Future State: Seamless Heterogeneous Modeling Environment

# Summary and Next Steps

- Platforms for digitally threaded design and verification of electronics are being piloted.

- Initial results are encouraging, as traditionally siloed tools show seamless interoperable potential.

- Standards adoption (e.g. SysML V2, FMI, OSLC) offers promise to realize expansion into multi-vendor DTDV platforms.

32<sup>nd</sup> Annual **INCOSE**

international symposium

hybrid event

**Detroit, MI, USA**

June 25 - 30, 2022

[www.incose.org/symp2022](http://www.incose.org/symp2022)